AN CONNECTOO PUBLICATION

**HDI PWB Reliability** by Paul Reid p.28

### ALSO:

PCBs for Medical

Applications—

A Designer's

Perspective

by Kenneth MacCallum p.38

### HIGH DENSITY INTERCONNECTS

### PCB BUYERScompare nearly 1900 manufacturers now at *The* PCB List.

Quick Search

Advanced Search

The best way to find a PCB fabricator, anywhere.

### **DESIGN NEWS**

### DFX — Design for Excellence

### Technical education with a design focus

### February 20-26, 2015

### IPC APEX EXPO in San Diego, CA

Premier industry event features a range of design offerings

- Professional development courses three hours of classroom instruction led by SMEs

- Design Forum a day of technical presentations from thought leaders in design

- · Designer Certification

### **IPC Designer Certification**

CID (Certified Interconnect Designer-Basic) and CID+ (Advanced) are valuable professional credentials, earned in three-day sessions that include classroom instruction and testing.

### **USA** sessions

February 20-22, 2015

CID and CID+

San Diego, CA in conjunction with IPC APEX EXPO

For USA sessions register at +1-800-643-7822.

New edition of CID and CID+ course materials will be available starting January 2015.

### If you are not already Certified:

Be sure to include the program in your budget for next year — contact your training center for information about class schedule and fees.

IPC Designers Council

Members Only

SUBSCRIBE

An international society for individuals with interest in design.

No fees, only benefits — like discounts on designated IPC documents.

Already in Designers Council? Be sure you can access the IPC technical forum for designers worldwide — subscribe at left.

### This Issue: HIGH DENSITY INTERCONNECTS

### FEATURED CONTENT

More and more designers are moving into the realm of HDI, which frees up real estate and allows more components to be placed on the board. This month, our expert HDI contributors explain the finer points of designing fine lines and blind and buried vias.

### **10 HDI Layer Stackups for Large, Dense PCBs** by Charles Pfeil and Happy Holden

### 28 HDI PWB Reliability by Paul Reid

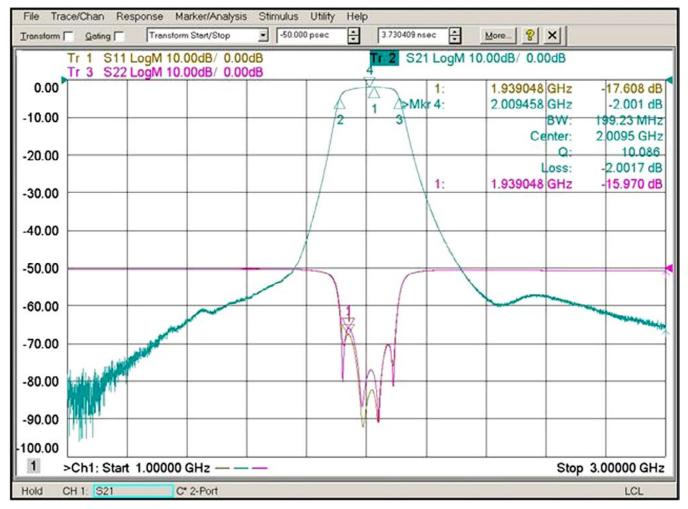

### Low-loss Laminate Materials for RF/Microwave/Millimeter-wave Designs

For over 100 years, Isola has been driving technology forward while improving end-product design with topperforming laminate and prepregs.

Our legacy continues with global R&D pushing our product line to the forefront in demanding RF/microwave designs.

With 10 manufacturing sites around the world, global quickturn capability, world-class technical service, measurement & modeling capabilities, and industry leading material development capabilities - Isola is well positioned to be your preferred RF/microwave partner.

The newest members of Isola's growing RF/Microwave laminate family now includes Terra Green™. a halogen-free, very low-loss, thermoset material that is available in a variety of laminate and prepreg offerings. This material is inexpensive to process – improving your company's bottom line, as well as the environment.

Astra®MT is a revolutionary ultra low-loss thermoset laminate replacement for PTFE, suitable for automotive radar, mm-wave and AESA applications.

I-Tera MT is available in core thicknesses from 0.002" to 0.018" and offers 18 different prepregs for optimal design flexibility.

I-Tera®MT RF is available in 20 and 30 mil cores and a 3.38 and 3.45 Dk.

|                                                                                                                                                                                                                                              | TerraGreen™     | Astra® MT       | I-Tera® MT/<br>I-Tera MT RF | IS680                                    |  |  |

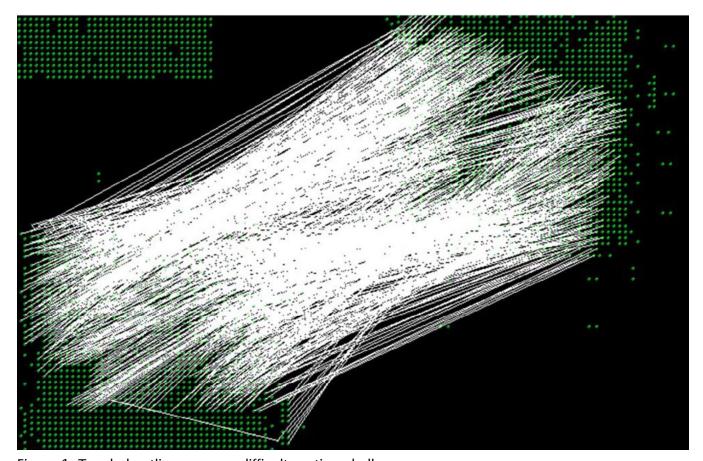

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|-----------------------------|------------------------------------------|--|--|

| Tg                                                                                                                                                                                                                                           | 200°C           | 200°C           | 200°C                       | 200°C                                    |  |  |

| Td                                                                                                                                                                                                                                           | 390°C           | 360°C           | 360°C                       | 360°C                                    |  |  |

| DK @ 10 GHz                                                                                                                                                                                                                                  | 3.45            | 3.00            | 3.45                        | 2.80 - 3.45                              |  |  |

| Df @ 10 GHz                                                                                                                                                                                                                                  | 0.0030          | 0.0017          | 0.0031                      | 0.0028 - 0.0036                          |  |  |

| CTE Z-axis (50 to 260°C)                                                                                                                                                                                                                     | 2.90%           | 2.90%           | 2.80%                       | 2.90%                                    |  |  |

| T-260 & T-288                                                                                                                                                                                                                                | >60             | >60             | >60                         | >60                                      |  |  |

| Halogen free                                                                                                                                                                                                                                 | Yes             | No              | No                          | No                                       |  |  |

| VLP-2 (2 micron Rz copper)                                                                                                                                                                                                                   | Standard        | Standard        | Available                   | Available                                |  |  |

| Stable Dk and Df over the temperature range                                                                                                                                                                                                  | -55°C to +125°C | -40°C to +140°C | -55°C to +125°C             | -55°C to +125°C                          |  |  |

| Optimized Global constructions for Pb-Free<br>Assembly                                                                                                                                                                                       | Yes             | Yes             | Yes                         | Yes                                      |  |  |

| Compatible with other Isola products for<br>hybrid designs                                                                                                                                                                                   | Yes             | Yes             | Yes                         | For use in double-<br>sided applications |  |  |

| Low PIM < -155 dBc                                                                                                                                                                                                                           | Yes             | Yes             | Yes                         | Yes                                      |  |  |

| NOTE: Dk Df is at one resin %. The data, while believed to be accurate and based on analytical methods considered to be reliable, is for information purposes only. Any sales of these products will be governed by the terms and conditions |                 |                 |                             |                                          |  |  |

of the agreement under which they are sold.

### FREE WEBINAR

### PCB Material Selection for RF/Microwave/Millimeter-wave Design

This webinar will educate you on how to select the appropriate PCB material for RF, microwave and millimeterwave applications through careful consideration of cost constraints and system-performance parameters, such as the frequency of operation and bandwidth, the electrical size of board and its critical features, loss and uniformity requirements, temperature range of system operation, and thermal and processing considerations.

DECEMBER 2014

**VOLUME 3**

NUMBER 12

MAGAZINE thepcbdesignmagazine.com

THE OPTIMUM

**MAGAZINE**

**DEDICATED TO**

**PCB DESIGN**

AN CONNECTOR PUBLICATION

### CONTENTS

38 PCBs for Medical Applications— A Designer's Perspective

by Kenneth MacCallum

### **COLUMNS**

8 IPC's Holiday Gift to Industry: Dieter 2.0

by Daniel J. Smith

46 Signal Integrity, Part 3 by Barry Olney

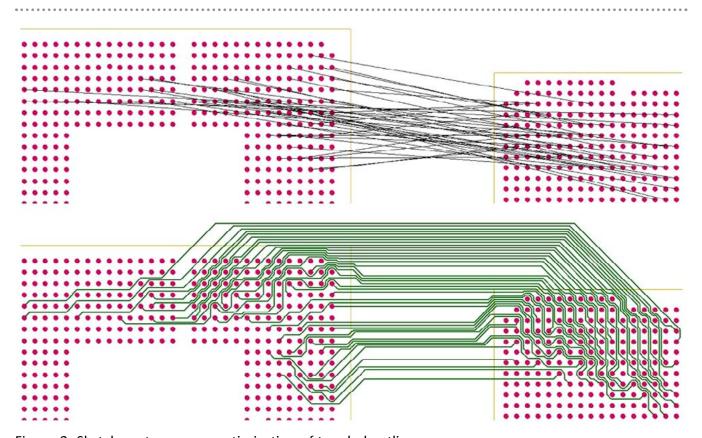

52 Sketch Routing, Part 3: Performance by Charles Pfeil

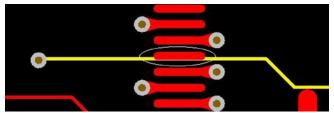

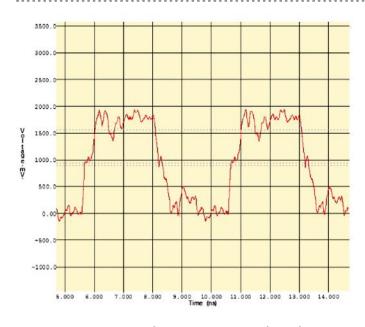

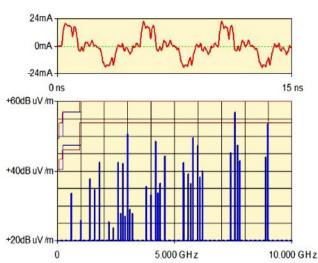

### 58 Making a Connection with **Conductor Discontinuities**

by John Coonrod

### 62 Like it or Not, You're a Role Model by Tim Haaq

### **VIDEO INTERVIEWS**

44 R&D and High-Tech Applications Set OEMs Apart

### **65** SMTA President Highlights Technical **Programs at SMTAI**

### **SHORT**

**26** Noise Floor for Ultrasensitive **Electronics Identified**

### **NEWS HIGHLIGHTS**

36 PCB007

56 Mil/Aero007

66 PCBDesign007

### **EXTRAS**

**68 Events Calendar**

69 Advertiser Index & Masthead

# THE BRAND NEW DATASHEET DIGESTING TIME SAVING HEADACHE AVOIDING LIBRARY BUILDER

### THE TOWN CRIER

### IPC's Holiday Gift to Industry: Dieter 2.0

by Daniel J. Smith RAYTHEON

We have all seen business leadership change as time passes. Some leaders have chosen to retire early, like Bill Gates of Microsoft, but some people have left us through death, such as Steve Jobs of Apple.

Both men were the icons, the "face" of their company's ups and downs. There was a succession plan in place to have a new leader take command, to continue the company's spirit and quality, but with a new vision. Each of their successors has also had his ups and downs, too, but they are the new face to those that buy and support those products.

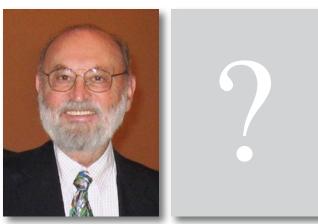

And then there was IPC's Dieter Bergman. Dieter was a caring, giving man to all he met. It did not matter if you agreed with him on every detail of a technology standard or topic;

you were in the presence of a man who gave his all for a company and an industry he truly loved.

Dieter was the "face of IPC," and it is to his empty pedestal that we all cast our gaze. This assembly of the curious is looking for the next icon of IPC's technology direction. That icon will be known simply as "Dieter 2.0."

I know that Dieter's assignments have been spread around within IPC to various people, staffers who may or may not have his SMEs (subject matter expert's) knowledge or passion. These assignments must be re-codified and reassigned back to the new person, Dieter 2.0. This will allow everyone to sigh with relief. We need a new standard-bearer for the thousands of volunteers who give up months of man-work-

### IPC'S HOLIDAY GIFT TO INDUSTRY: DIETER 2.0 continues

Figure 1: Dieter Bergman left a void in the industry. Who will be Dieter 2.0?

hours every year for creating IPC standards for Paul Eisler's industry.

So, just as a child assembles his Christmas list, I have created a similar wish list of who I believe IPC needs to seek out to be their next IPC representative:

- 1) A visionary: The person needs to examine the previous vision of where IPC was going, but also have a new vision of what both IPC and the industry requires in order to be productive and a continuing presence and force.

- 2) A selfless team player: This person should be one who listens and builds consensus for the good of the entire PCB industry, and not be driven by a personal or hidden agenda.

- 3) A technologist: This person should have acquired a majority of their cognitive knowledge from spending time in the trenches of this industry. There is no amount of reading that will prepare this person for what is truly needed to understand the chemistry of fabrication and assembly knowledge, as well as why the IPC standards have been authored in the manner they have for all of these years.

- 4) A historian: Dieter 2.0 must understand the history of where IPC has been. This will prove critical to formulating our collective direction going forward. It will be important to avoid "rat holes" of previous initiatives that have produced little or negative progress for IPC and the industry.

- 5) A listener: The majority of IPC is made

up of participants from all aspects of the PCB design process. Every participant has a voice and an idea that needs to be shared and heard. This person needs to let these ideas come out and help shape the overall direction of our future.

6) A consensus builder: Dieter 2.0 must sort out all of this information from the participants, and use their powers of communication to ensure that a collective direction forward on a subject has the support of the majority—for the good of the majority.

It would be great if there was a "recipe" for creating a clone of Dieter. But, as we all know, it is more important to be your own true leader than be just like your predecessor.

Dale Sevrey, one of my many managers over the years, offered me sound personal advice regarding death: "Everyone grieves differently."

In reflecting on Dale's words, I cannot rush IPC to hurry this grieving process. I respect everyone who works within (and for) this organization. I can only offer one request:

If the grieving process has completed, it would be a great present to the industry if you would select a person to be our future "presence."

If Dieter 2.0 could first be announced, and then formally introduced at IPC APEX EXPO 2015, I am sure there would be a surge in attendance just to meet and greet this new technologist and continue their allegiance to volunteering for IPC.

I wish all of you a happy and safe holiday season with time to reflect on the joys and sorrows of this past year, and to offer thanks in prayer in anticipation of a great future for all in the coming year. **PCBDESIGN**

Daniel J. Smith is a principal technologist for Raytheon Missile Systems. He has taught multiple aspects of the PCB design process internationally, and he has authored several PCB-related patents, articles,

and standards over the past 30+ years. To contact Smith, click here.

by Charles Pfeil

MENTOR GRAPHICS

### **Happy Holden**

CONSULTANT

This article is intended to help those who are doing large, dense PCBs with multiple high pin-count BGAs, and finding standard laminate stackups inadequate to meet their cost and performance goals. Maybe your laminate board has too many layers, or the feature sizes prevent effective breakout and routing of the BGAs. HDI stackups are a viable alternative and can provide lower cost with higher performance if designed properly.

Hopefully from this article you will be able to determine which stackup methodology is best for your designs and why the alternatives may not be appropriate. To find out which stackups are recommended, you can skip to the end of the document. However, if you want to understand the reasons why these stackups are recommended and the impact of choosing one of the alternatives, then it would be best to read the whole article.

Defining the appropriate stackup should be considered as one of the most important aspects of initial design work. Since there are so many variables involved with stackups, this article will focus on stackups that will enable effective design of boards with multiple large, dense BGAs. Typically this includes boards for the networking, computer, server, and emulation marketplace. It is assumed that even though handheld devices and consumer electronic products will likely have dense BGAs, it is unusual for them to have multiple instances exceeding 1500 pins and as such, do not present the kind of design challenges of concern herein.

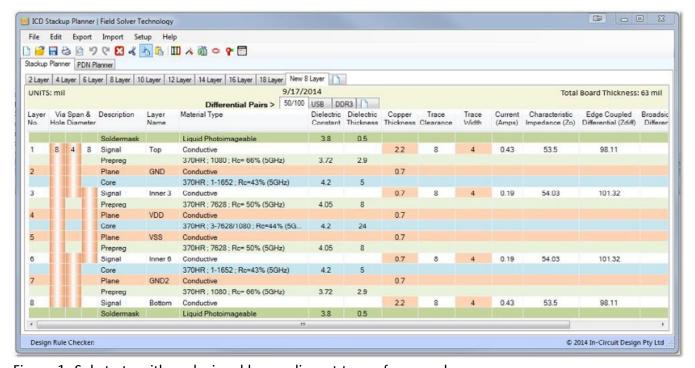

### **Fabricators**

Stackups should be designed in conjunction with the fabrication vendor to minimize cost and meet signal integrity requirements. The board fabrication vendor ultimately builds a board that meets your requirements for cost, reliability, overall thickness, and impedance control. There may be additional requirements related to plating and specific materials. As a general rule, the vendor will adjust all the stackup variables as needed during their process to meet your goals. The most productive method is to agree with the vendor on a stackup prior to designing the board; then, the fabricator will need to make minimal adjustments to meet your goals.

Consider impedance control. Regardless of how carefully the stackup is defined with trace widths, material choices, dielectric and cop-

### A HIGHER DEGREE OF THERMAL CONDUCTIVITY, WHERE AND WHEN YOU NEED IT.

|        | Thermal<br>Conductivity | Ceramic<br>Filled | Fully<br>Formable | Non-Glass<br>Reinforced | Halogen<br>Free |

|--------|-------------------------|-------------------|-------------------|-------------------------|-----------------|

| VT-44A | 1.0W/m.K.               | <b>V</b>          |                   |                         |                 |

| VT-4A1 | 1.6W/m.K.               | <b>V</b>          |                   |                         |                 |

| VT-4A2 | 2.2W/m.K.               | <b>V</b>          |                   |                         |                 |

| VT-4B1 | 1.0W/m.K.               | <b>V</b>          |                   |                         |                 |

| VT-4B3 | 3.0W/m.K.               | <b>V</b>          |                   |                         |                 |

| VT-4B5 | 4.2W/m.K.               | <b>/</b>          |                   |                         |                 |

| VT-4B7 | 6.5W/m.K.               |                   |                   |                         |                 |

**VIEW THERMAL MANAGEMENT PRODUCTS**

Wherever technology takes you, we deliver.

per thicknesses, the fabrication process is not so exact. Each vendor has different equipment and methods. The lamination process shrinks the dielectrics and materials may be changed if not in stock or readily available. The tolerances in all areas add up and ultimately a reliable vendor has to make the right combination of adjustments in-process so that when measuring impedance on the test coupon, it fulfills your spec. Trace widths and material thicknesses may change a little, but if the measured impedance is within spec then it really doesn't matter what changes were made, as long as the other requirements are not fatally compromised, of

If the initial stackup is not defined properly, minor acceptable adjustments by the fabrication vendor will not be adequate to fulfill your overall requirements. A wise and experienced vendor will not accept the risk of making major changes to the design data.

### **Dependencies**

Unfortunately there are many dependencies, some of them circular when defining a stackup. The process of determining an effective stackup can be overwhelming. Forgive the next meandering and confusing paragraph, but this is a good example of the difficult process of deciding which variables need to be compromised or emphasized to reach your goals. It is necessary to reduce the layer count to keep costs down. On some of the largest PCBs, there are well over 10,000 nets, which require many layers for routing. To control crosstalk, you need to increase the spacing between traces which will likely necessitate even more layers. You may also want to run the diff pairs together through the via array under the BGA, which means the via must be small enough to not only allow the diff pair to run together, but also space the traces far enough apart to attain the desired coupling.

These traces also need to be the appropriate width in correlation to the thickness of the dielectrics and their material attributes to provide the desired impedance. But if you have too many layers, then the via needs to be bigger otherwise the aspect ratio of hole size to length becomes too great to drill with a good yield. If you make the via hole smaller, you can enable more dense routing but may sacrifice manufacturing yields. If you make the via hole larger, you may have to split the diff pairs through the BGA fanout via array and negatively impact your signal integrity. If you have more layers because you have to split the diff pairs, you will need an even larger via. On top of that, all these factors may require you to develop special fanout patterns in the context of the stackup to support the manufacturing, signal integrity and routing goals. This paragraph touches just a few of the dependencies, yet even so, it describes a daunting task.

Where does one start, then? Later, you will see a number of example stackups with their advantages and disadvantages, plus a basic description of which via models and design rules work best. Some signal and power integrity concerns will also be addressed.

### **Overview of Stackup Types**

In the context of boards that have high pincount BGAs, there are three stackup types of interest:

### 1. Standard Lamination with Through Vias

### Advantages

- Low cost (until layer count becomes too high).

- Simple via models.

- Simple dielectrics—primarily FR-4.

- Mature process. "Everybody does it."

- High reliability (until layer count becomes too high).

### Disadvantages

- If layer count becomes too high.

- Fewer fabrication vendors can obtain good yields, costs skyrocket.

- Can delaminate under high temperatures required for ROHS lead-free soldering.

- Via has to be large, reducing route-ability, increasing layers.

- Difficult to implement for BGA pinpitches below 1 mm.

- Through-hole vias capacitively couple to every plane layer, and signal losses increase with thickness.

- Long via stubs create impedance mismatches, reflections on single-ended

- Large via pads often force diff pairs to be split under BGAs.

### Recommendations

There are a number of tipping points where standard lamination with through vias is not viable:

- Once the board is over 28 layers, it becomes difficult to manufacture with acceptable yields and therefore can become cost-prohibitive.

- If the board is over 28 layers, the dielectrics can be so thin that delamination can occur under the higher temperatures required for lead-free soldering.

- Generally when using a few BGAs with less than 1500 pins and a 1mm pin-pitch, the breakout and routing of these devices is feasible using through vias. However, if you have a large number of these on a single design, then the route density may force the layer count up high enough to limit the effectiveness of this stackup. If you have multiple BGAs with over 1500 pins and 0.8mm pin-pitch (or less) it is likely that through vias will make it very difficult to route these devices.

- When the thickness of the board, due to the number of layers, forces the via to be so large that it inhibits routability. Via length to hole diameter should be <10x, or reliability will decline significantly. Pad diameter should be hole size plus 0.01". If the via pad is so large that it prevents diff pairs or multiple singleended traces from being routed between the BGA via arrays, then more layers will be required to complete the routing. Vias can be shifted off the standard matrix under BGAs; however, with through vias, not much is gained.

### 2. Sequential Lamination with Blind and Buried Vias

### Advantages

- Potentially shorter via stubs.

- Fairly simple via models.

- Generally smaller vias than required for through hole vias. Minimum size for mechanically drilled vias are the same as for standard laminate; however, blind and buried vias will likely have a smaller aspect ratio, enabling more use of minimum via hole size, which is 8th.

- Simple dielectrics, primarily FR-4.

- Effective use of blind & buried vias opens up routing channels, potential for fewer layers.

### Disadvantages

- Not a widely adopted process; more and more fabricators do HDI instead.

- Minimum size for drilled vias is 8th.

- Costs more than through hole laminated, yet minimum trace widths are still the same.

- Practical reliability limits the number of sequential laminations to 2 or 3.

### Recommendations

- Sequentially laminated boards have the same tipping points as standard laminates; however, since the via length to hole size aspect ratio will be less and pad sizes can be smaller, routability improves and it is less likely that the design would exceed 28 layers.

- Since the feature sizes for traces can vias are still the same as with standard laminate, designing with multiple large BGAs of < 1 mm is very difficult.

### 3. Buildup with Microvias (HDI)

### Advantages

- Smaller feature sizes for vias and traces en able higher route density and fewer layers.

- Effective use of microvia patterns opens up routing channels, potential for fewer lavers.

- Only practical way to design with multiple large BGAs having <0.8 mm pitch.

- Lowest cost for high density boards.

- Improved signal and power integrity, with appropriate stackup definition.

- Materials do well in processes requiring RoHS.

- Newer materials are available at higher performance and lower costs. These new materials are not suitable for standard or sequential lamination.

### Disadvantages

- Complex via models—many variations and still evolving.

- Complex stackup definition.

- Effective design methods on large dense designs have not been widely understood and documentation is sparse.

- Predictive design guides and cost estimates not yet available.

- Although HDI fabrication is pervasive in the Pacific Rim and China, North America has been slow to adopt.

### Recommendations

- HDI is the best alternative to high layercount and expensive standard laminate or sequentially laminated boards.

- The trend is for higher pin-count and finer pin pitch. The tipping point will occur when the >1500 pin BGAs use a .8 mm pitch. The only way to effectively breakout and route multiple instances of these devices on a single board will be with the smaller HDI feature sizes.

- HDI currently dominates the fabrication technology for handheld and consumer electronics. For large board designs, it will continue to grow.

### **HDI Stackup Details**

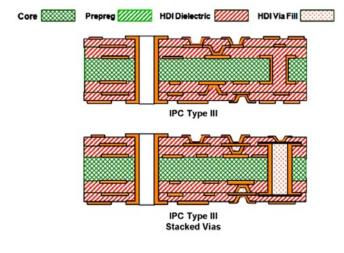

This section is provided as a reference describing the relevant HDI stackup information based on the IPC standard. In this section, Types I, II and III are described. Type III is the recommended configuration for large, dense boards with multiple high pin-count BGAs.

### **IPC-2315 Design Guide for High Density Interconnects and Microvias**

Published jointly with the Japan Printed Circuits Association, IPC/JPCA-2315 provides an easy-to-follow tutorial on the selection of HDI and microvia design rules and structures. It addresses various considerations when designing an HDI printed wiring board, including design examples and processes, selection of materials, general descriptions, and various microvia technologies. It offers designers and manufacturers one source for reliable design and manufacturability information for commonly produced HDI boards.

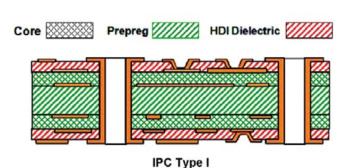

### **HDI Type I**

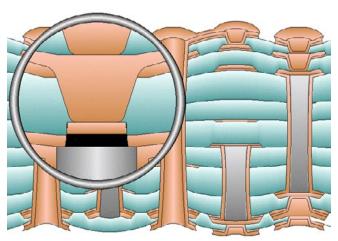

This construction uses both microvias and through vias in a structure consisting of a laminated core and a single micro via layer on at least one side.

### Notes:

- 1. The number of layers in the laminated core varies and is limited by two factors

- a. The through-via should have an aspect ratio (total length to hole size) less than 10x to maintain reasonable reliability.

- b. If the FR-4 dielectrics become too thin, they will delaminate under higher temperatures required for lead-free soldering.

### Recommendations

• In the context of large dense boards with multiple high pin-count BGAs, this stackup will not be significantly better than laminate. The through via pads will need to be large. Using only a single microvia layer will limit the ability to benefit from the smaller via and trace feature sizes.

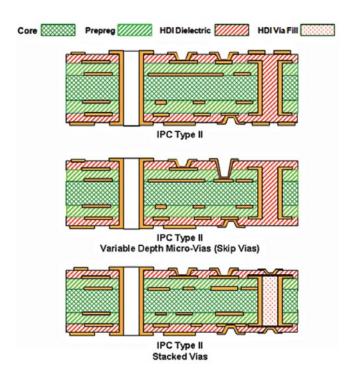

### **HDI Type II**

This construction uses microvias, buried vias, and may have through vias.

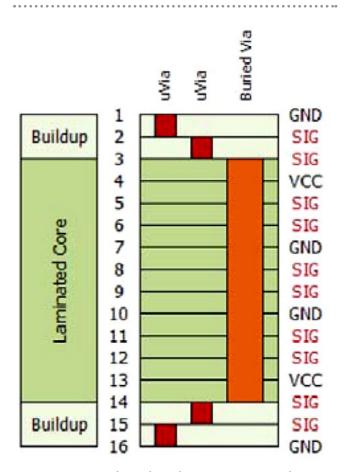

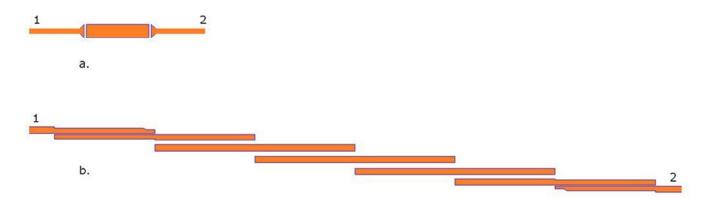

Figure 1: IPC Type I construction.

### How can you find the best PCB Partner? We can tell you. We wrote the book on it.

Choosing a PCB partner isn't hard—if you know what to look for. We've broken it down into "The 5 Commandments" and you can download it for free.

We are proud to be the Circuit Board Manufacturer of more than 400 growing companies, and even prouder to be a good partner for all our customers!

Click to Download

U.S. Circuit, Incorporated 2071 Wineridge Place Escondido, CA 92029 +1 (760) 489-1413 www.uscircuit.com

Figure 2: Various kinds of IPC Type II construction.

- There is a single microvia layer on at least one side.

- Via holes are drilled in a laminated core and become buried when the dielectric material is added for the microvias.

- Microvias are staggered from other microvias and may be stacked or staggered relative to the buried vias.

**Additional note:** See Type I note on limiting the number of laminated core layers, which applies to all variations of Type II through and buried vias.

### Recommendations

- In the context of large dense boards with multiple high pin-count BGAs, this stackup is better than Type I; however, it is not adequate for the more difficult designs. Using buried vias instead of the through vias is a significant advantage. Using only a single microvia layer will limit the ability to benefit from the smaller via and trace feature sizes.

- The single microvia layer also restricts

Figure 3: Example of IPC Type III construction.

the viability of using the outer layers for a GND plane. Having only one buildup layer for routing traces isn't nearly as effective as two.

### **HDI Type III**

This construction uses microvias, buried vias, and may have through vias.

- There are at least two microvia layers on at least one side.

- Via holes are drilled in a laminated core and become buried when the dielectric material is added for the microvias.

- Microvias may be staggered or stacked with buried vias.

**Additional note:** See Type I note on limiting the number of laminated core layers which applies to all variations of Type III through and buried vias.

### Recommendations

- HDI Type III is the best stackup configuration for large dense boards with multiple high pincount BGAs.

- With two microvia layers there is considerable routing area available using the smaller via and trace feature sizes.

- Using the outer layers for a GND plane is feasible because there are still enough microvia layers available for signal routing.

## MEC FROM UIC

**OPTIMUM TOPOGRAPHY**

**ULTIMATE ADHESION**

**EXCEPTIONAL FLEXIBILITY**

- \* FlatBOND GT Ultimate signal integrity meets ultimate board integrity in this treatment for 25 GHz+ designs. High adhesion with insulation materials; sufficient adhesion for low dielectric resins.

- \* V-Bond 7710 Exceptional inner layer adhesion, substantial cost and maintenance advantages compared with oxide alternatives; flat immersion or spray compatible, broad temperature range.

**EtchBOND CZ-5480** The industry standard bearer for equipment and process flow compatibility; substantially superior to peroxide sulfuric microetchants.

**2030 EtchBOND** The elite adhesion performer provides highest roughness with least material removal.

Uyemura is committed to providing its customers with significant advantages in performance, cost, and maintenance, and to supporting each program with the industry's finest technical support.

For details on MEC products, or to arrange test processing, contact meonta@uyemura.com.

\*Now available for the first time in North America.

UYEMURA USA www.uyemura.com

• Using stacked vias will allow for greater route density; however, the cost will be higher.

### HDI Type IV, V, VI

These additional HDI Types are defined in the IPC-2315 specification; however, they are not presented here simply because they are more expensive to fabricate and are probably not necessary for large, dense PCBs with BGA breakout and routing challenges.

### **Via Models**

HDI Type III accommodates numerous via models and spans. Ultimately the via model that suits your design best will be driven by finding the least expensive method that will still enable adequate route density within the constraints of signal integrity.

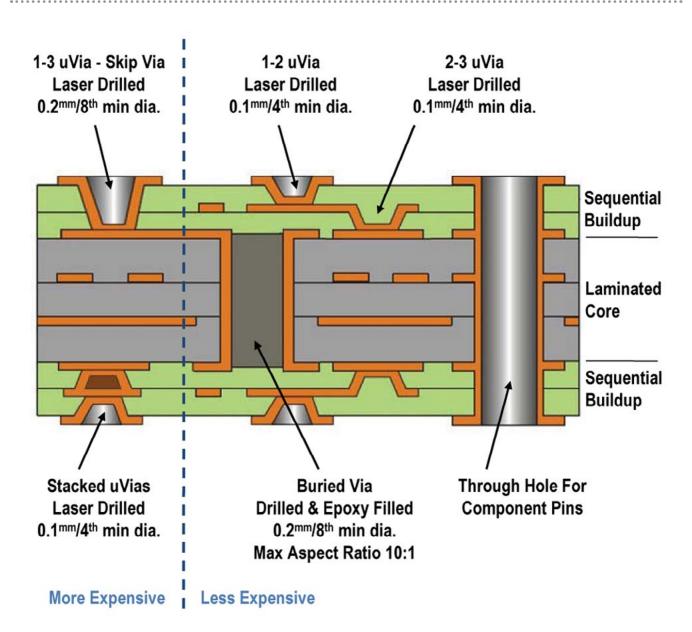

The graphic in Figure 4 presents some of the via models that may be used in HDI Type III.

Figure 4: Examples of Type III construction.

- Skip vias: This via model is effective for transitioning layers (because it emulates the stacked via); however it is not as efficient as stacked vias for route space due to the fact that the minimum diameter is 8th.

- Buried vias: As a general rule, all unused pads on the buried vias should be removed. This will significantly reduce the crosstalk.

- Microvia pad sizes: Although the pad size will vary by fabricator, using a pad .15mm/6th larger than the hole is adequate.

- Via aspect ratio: Hole length to diameter for microvias is 5:1; for buried vias, 10:1.

### **Alternative Via Spans**

### **Stacking Microvias and Buried Vias**

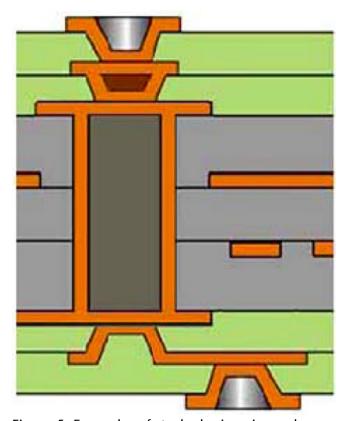

As seen in Figure 5, the microvias may be stacked upon each other, and/or with buried vias.

Figure 5: Examples of stacked microvias and buried vias.

### Advantages

Using stacked vias enables the most flexible and efficient via configuration for routing.

### Disadvantages

• Stacking vias generally costs more due to the additional steps required to ensure a good connection between the vias.

### **Extending Buried Vias**

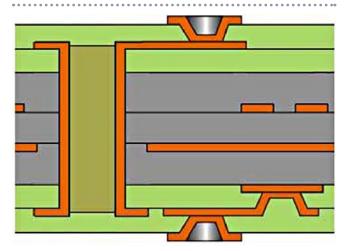

As seen in Figure 6, you can extend the buried via into the first microvia layer.

### Advantages

If you have power and ground nets that need to extend all the way through the board, using extended buried via uses less space.

### Disadvantages

- Single-ended nets that use the extended blind via may suffer from additional via-stub effects; however, the additional stub length may be insignificant depending on the frequency.

- Depending on the fabricator, the cost of extending the buried-via may be slightly more than just having the buried-via in the laminated core.

### **Layer Count**

The number of buildup and core layers required to route the board and fulfill the per-

Figure 6: Example of a buried via extended into the first microvia layer.

formance and signal integrity requirements will vary depending on the route density and manner in which you decide to manage the plane layer assignments. Determining the route density is a subject outside the scope of this article; however, as a general rule for large, dense boards, start with 8-10 signal layers and increase them as needed during the routing process.

Since the thickness of the laminated core will be limited by the aspect ratio of the buried via (10:1), work with your board fabricator to determine core and prepreg thicknesses. Doing this in conjunction with trying to minimize via pad size for routing will enable you to determine the high-end number of layers available in the laminated core.

### **Design Rules**

Throughout this paper, the minimum values for via hole sizes, pad sizes and the aspect ratios have been described. These minimums are used as a guide to enable high yields. Minimum trace widths and clearances are based upon the fabricator's capabilities; however, are more than likely to be set based on signal integrity requirements such as impedance control and minimizing crosstalk.

### **Fanout Patterns**

The method used for fanout of BGAs is a subject worthy of its own article, and can significantly contribute to the success or failure of the design. Here are some considerations:

### Via location relative to BGA pad

- Adjacent (dog-bone)

- Partial via-in-pad

- Offset via-in-pad

- Via-in-pad

When using a combination of microvias and buried vias, each via span can have its own pattern within the BGA and as such can affect the routability of the device.

- Via-in-pad methods provide the greatest opportunity to increase route density.

- Shifting and aligning the vias is likely to improve routability.

- Using complementary patterns for the

- microvias and buried vias can improve routability

- The goal should be to reduce the overall "effective" number of pins by the time you get to the laminated core, thus reducing the number of layers required to breakout and route the BGA.

### **Recommended Stackup Criteria**

A primary driver for going to HDI is to obtain sufficient route density to reduce layer count, thus lowering costs and improving reliability. Yet this must be done while maintaining power and signal integrity. Cost, density, power and signal integrity are the factors used in this paper to determine which stackups are recommended.

### **HDI Cost**

There are four drivers that determine the fabrication cost for HDI boards.

- Materials: Not only the type of material used but also the amount. So obviously a larger board will cost more than a smaller one.

- Laminations: The more lamination steps, the higher the cost. When buildup layers and via spans are mirrored about the core, then they can be done in the same lamination step. As you will see in the recommended stackups, the manner in which the via spans are defined affects the number of laminations.

- Drills: The more drill setups required, the higher the cost. A through-hole, buried via and a microvia each count as single drill setup. When buildup layers and via spans are mirrored about the core, then the microvia drilling on both sides is considered as one drill setup. The manner in which the via spans are defined affects the number of drill setups.

- Plating: Plating steps affects the cost, the more steps the higher the cost. These steps are used to plate the via wall and to ensure a reliable connection at the bottom of the drill. Using stacked vias and additional buildup layers generally increases the number of plating steps.

## We see a future with no substrate restrictions, higher yield and shorter fabrication times.

Our partnership with eSurface will give designers more creativity without compromising manufacturing viability.

### Key eSurface advantages include:

- Improved line geometries down to .002 and less

- Improved Signal Integrity

- Ideally suited for RF and High-Speed applications

- Improved bond between the copper and the laminate

- The ability to adhere to almost any surface material.

- Increased circuit density, improved manufacturability, reduced lead time and thus reduced cost

Murrietta Circuits is proud to be an eSurface Licensed Manufacturer

Click to learn more

### **Route Density**

Microvias and smaller trace widths on buildup layers can significantly improve route density. Via-in-pad and stacking vias is also very good for improving route density. Using microvias and blind vias in certain patterns can open considerable space for routing on the laminate core layers. Ultimately, increasing route density will reduce your layer count and overall fabrication costs.

### Power Integrity

In the context of an HDI Type III stackup, location of the planes will impact your power distribution and integrity along with signal integrity. The appropriate location of planes is a much deeper and more complicated subject than can be addressed in this article; however, certain methodologies are recognized as effective and will be described at a high level here.

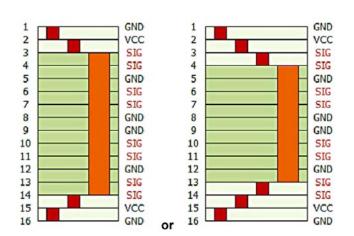

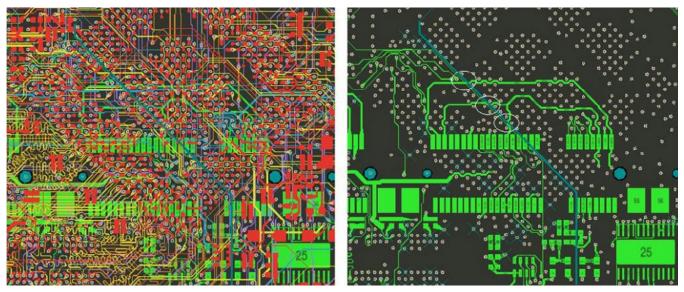

Figure 7: Typical stackup for GND assigned to outer layers.

In the stackups shown in Figures 7 and 8, the number of layers in the laminated core is variable; 16 layers is just convenient for the purpose of depicting plane layer assignments graphically.

Outer Layer GND: A stackup such as this is typical when GND is assigned to the outer lavers.

### Advantages

- GND on the outer layers provide an excellent EMI shield.

- If you can place the bypass capacitors for the BGA on the same layer as the BGA, then you can minimize the number of vias used for GND underneath the BGA. This will open routing channels which may be critical for an extremely dense board. You may still want vias for some of the GND pins to improve the return paths.

### Disadvantages

- If you manage your return paths with an appropriate but not excessive number of GND vias under the BGA, then there really isn't a downside to using this method.

- Some may say that using the outer layers for GND will limit the number of buildup (smaller features) layers for routing signals. Although this is true, it is also important to consider that controlling the signal integrity of those nets will be more difficult and burying the first GND plane in the laminate structure will result in the routing on the microvia layers not having a good reference plane.

Outer Layer GND & VCC: A stackup such as this one is typical when GND and VCC are assigned to the outer layers.

**Note:** Using stacked vias would be good for this kind of stackup if it can be cost-justified.

### Advantages

Same advantages as listed for Outer Layer GND, plus these additional benefits:

• The capacitive coupling between the GND and VCC layers will be excellent,

- minimizing the bypass capacitors needed for the BGA (assuming you use a relatively thin dielectric, less than .05 mm).

- This is also an opportunity to use embedded capacitors and pull-up resistors effectively. Considerable routing space would be opened on all signal layers.

### Disadvantages

If you manage your return paths with an appropriate but not excessive number of GND vias under the BGA, then there really isn't a downside to using this method.

Split Planes: Often large BGAs require multiple voltage supplies. You can use split planes or dedicated voltage layers for this power distribution. It would be best to add a couple of voltage supply layers in the center of the board, surrounded by GND planes to avoid having signal layers affected by crossing the splits or different voltages.

### Signal Integrity

This is a subject that has many dependencies, variables and thousands of articles. No attempt here to do anything but point out a few design methods related to large HDI stackups that will positively affect signal integrity.

- Remove unused pads on buried vias. This will reduce crosstalk significantly.

- Route the high-speed single-ended nets

Figure 8: Typical stackup for GND and VCC assigned to outer layers.

- on the buildup layers closest to the component. Stub effects are eliminated because buried vias are not used.

- Route diff pairs on the laminated core layers. The via stubs affect the diff pairs less than the single-ended nets and the crosstalk between the diff pair vias (if the unused pads are removed) is likely to be insignificant.

- A stripline configuration where pairs of signal layers are sandwiched between plane layers not only provides the best return paths but also reduce crosstalk. This supports the notion that using a GND plane on the outer layers is a good practice.

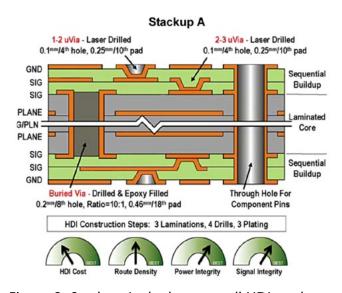

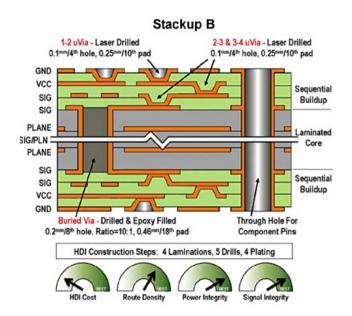

### Recommended HDI Type III Stackups

What are the best HDI stackups? It depends on your priorities. These stackups were analyzed for relative cost, route density, power integrity and signal integrity. The following three are rated A, B, and C, with the priority given to route density with good power and signal integrity.

### Stackup A comments:

• This is a good average of the variables and a great stackup to start with if this is your first attempt at HDI.

Figure 9: Stackup A, the best overall HDI stackup of the group.

Figure 10: Stackup B, another good HDI stackup.

- The via models are simple and it won't be difficult to find vendors who can fabricate it.

- The GND plane on the outer layers provides a high rating for power and signal integrity.

### Stackup B comments:

- The GND and VCC on the outer layers provide the best power and signal integrity.

- The additional buildup layer increases the cost (more laminations, drills and plating steps) but also improves the route density as opposed to losing an HDI

- routing layer due to the VCC plane.

- The via models are simple and it won't be difficult to find vendors who can fabricate it.

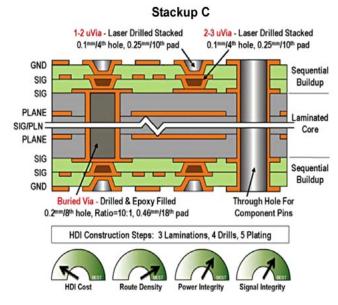

### Stackup C comments:

- The stacked vias enable the best route density but also increases the cost and may limit the number of vendors who can fabricate this stackup.

- The GND plane on the outer layers provides the high rating for power and signal integrity.

Figure 11: Stackup C, also a good HDI stackup.

Figure 12: Stackup D, a secondary HDI stackup.

### **Secondary HDI Stackups**

These stackups are useful in their own way, depending on your priorities, but they are not as good overall as the Top 3.

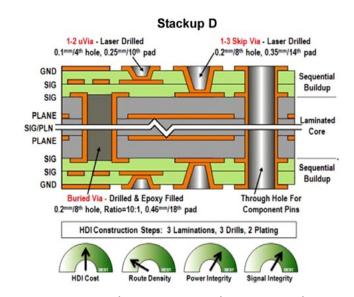

### Stackup D comments:

• The GND plane on the outer layers provides a high rating for power and signal integrity.

Figure 13: Stackup E, another secondary HDI stackup.

Figure 14: Stackup F, another secondary HDI stackup.

Figure 15: Stackup G, a final secondary HDI stackup.

• The skip via reduces laminations and plating steps, which lowers cost; however, this contributes to a relatively low route density.

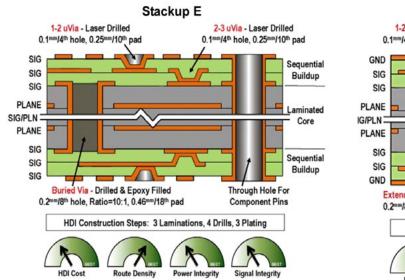

### Stackup E comments:

- The via models are simple and it won't be difficult to find vendors who can fabricate it.

- The lack of a GND plane on the outer layers reduces power and signal integrity; however, it does provide for improved route density assuming routing would be done on the outer layers.

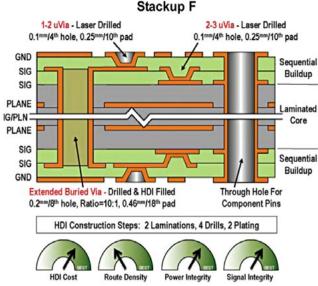

### Stackup F comments:

- The GND plane on the outer layers provides the high rating for power and signal integrity.

- The extended buried via reduces lamination and plating steps, which lowers cost; however, it also reduces route density.

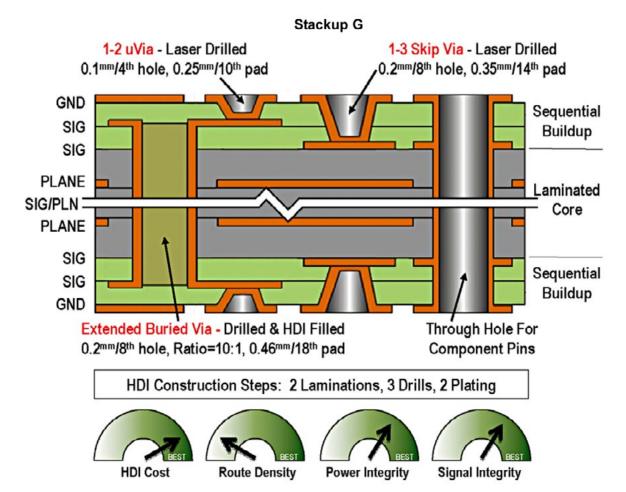

### Stackup G comments:

- The GND plane on the outer layers provides the high rating for power and signal integrity.

- The extended buried via and the skip via reduces the lamination and plating

steps which lowers cost; however it also reduces route density. PCBDESIGN

Charles Pfeil is an engineering director in the Systems Design Division at Mentor Graphics. He was the original product architect for Xpedition PCB and an inventor of XtremePCB. Pfeil has

been in the PCB industry over 40 years as a designer, owner of a service bureau, and has also worked in marketing and engineering management at Racal-Redac, ASI, Cadence, PADS, and VeriBest. To contact him, click here.

Happy Holden has been working with printed circuits in various capacities since 1970. He retired from Hewlett-Packard after nearly 29 years, and was senior PCB technologist for Mentor Graphics'

System Design Division. Happy also served as a senior technologist with Foxconn and Gentex before retiring, finally, in 2013. He's currently working with Clyde Coombs on the 7th edition of the PCB Handbook, due out in mid-2015. To contact him, click here.

### Noise Floor for Ultrasensitive **Electronics Identified**

A team of engineers and scientists has identified a source of electronic noise that could affect the functioning of instruments operating at very low temperature. The findings, detailed in the journal Na-

ture Materials, could have implications for the future design of transistors and other electronic components.

The electronic noise the team identified is related to the temperature of the electrons in a given device, which in turn is governed by heat transfer due to packets of vibrational energy, called phonons, that are present in all crystals.

"A phonon is similar to a photon, which is a discrete packet of light," says Austin Minnich, an assistant professor of mechanical engineering and applied physics in Caltech's Division of Engineering and Applied Science and corresponding author of the new paper.

One way that engineers have traditionally reduced phonon scattering is to use high-quality materials that contain as few defects as possible. A more common solution, however, is to operate

> electronics in extremely cold conditions because scattering drops off dramatically when the temperature dips below about 50 kelvins, or about -370 degrees Fahrenheit.

> "We don't know what the precise strategy will be yet, but now we know the direction we should be going. That's an improvement."

## The Absolute Best Value in High Technology Printed Circuit Boards

Since 1979, Eagle Electronics Inc. has provided our Customers with the highest quality Printed Circuit Boards at fair and competitive prices. We are committed to exceeding our Customers' expectations and requirements, acheiving total customer satisfaction on each and every job. It's just the way we do business!

With Eagle, you can expect:

- Rapid Response to Quote Requests

- Fair and Competitive Pricing/Costs

- 100% Quality Performance

- 100% On-Time Delivery Performance

- Flexibility Scheduling

- Stock/Consigned Inventory Programs

- Thorough follow-up after job completion

- Total Satisfaction!

click here for a virtual tour of our facility!

www.eagle-elec.com

### by Paul Reid

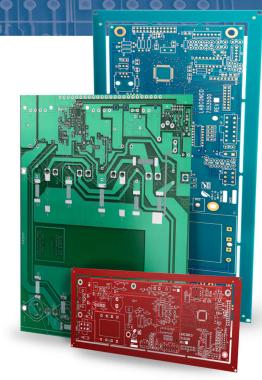

An HDI PWB may be defined as a PWB with a higher wiring density per unit area than conventional PWB. They have smaller lines and spaces, smaller vias and capture pads and higher connection pad density than employed in conventional PWB technology. HDI boards utilize microvias, buried vias and sequential lamination with insulation materials and conductor wiring for higher routing density. HDI is an alternative to high layer-count and standard laminate or sequentially laminated boards.

HDI boards are characterized by high-density attributes including laser microvias, fine lines, smaller grid sizes and high performance thin materials. This increased density enables more functionality per unit area. Higher technology HDI PWBs have multiple layers of copper-filled, stacked microvias, which create a structure that enables even more complex interconnections. These very complex structures provide the necessary routing solutions for today's large pin-count chips utilized in mobile devices and other high technology products.

When it comes to HDI reliability, what we must do is consider two parts: the copper interconnects and the base material. What one can do is test the reliability with thermal cycling using Interconnect Stress Test (IST) coupons. The IST coupon tests the copper interconnection and checks for material damage. The coupon is fabricated on the production panel with the PWBs and has all the attributes of the PWB. So the coupon has the same construction, copper weights, hole sizes, grid sizes, and copper plating as is found in the corresponding board. The test thermal cycles the IST coupon, typically for 500 cycles, or until the coupon fails with a 10% increase in resistance due to cracks that develop in copper interconnections as a result of thermal cycling.

By measuring capacitance change between ground planes, we can determine if there is any significant material damage in the coupon. One must measure the capacitance in picofarads between adjacent ground planes before testing (to establish a base line), after preconditioning (a simulation of assembly and rework) and at the end of test. We then compare the measurement after preconditioning and at the end of test to

### INTRODUCING COOLSPAN® TECA

thermally & electrically conductive adhesive

### Rogers can help by being your reliable conductive adhesive film source

Get the heat out of those high-power PCBs. COOLSPAN® Thermally & Electrically Conductive Adhesive (TECA) Films are ideal for dissipating heat in high-frequency circuits. COOLSPAN adhesives feature outstanding thermal conductivity (6 W/m/K) and reliable thermal stability. Keep things cool, with Rogers and COOLSPAN TECA film.

> **CONTACT YOUR SUPPORT TEAM TODAY**

www.rogerscorp.com

### MEET YOUR COOLSPAN® **TECA FILM SUPPORT TEAM**

Leading the way in...

• Support • Service • Knowledge • Reputation

### SCAN THE CODE TO GET OUR CONTACT INFO.

Dale Doyle Western Territory

John Dobrick

Scott Kennedy

John Hendricks

**Kent Yeung** Regional

Sales Director

If you are unable to scan a VR code please visit our Support Team website at www.rogerscorp.com/coolspan

### **HDI PWB RELIABILITY** continues

those original readings. A -4% change or greater indicates significant material damage and a cross section is processed to confirm or refute this finding.

The major problem is the implementation of lead-free soldering that requires assembly temperatures of 260°C. The FR-4 material is at its limit to withstand the heat when exposed to 260°C. The Z-axis expansion is at its highest at this temperature, putting extra strain on the copper interconnects.

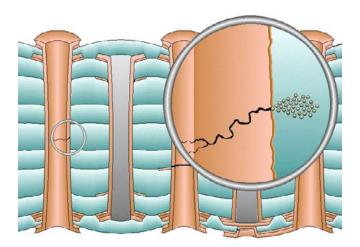

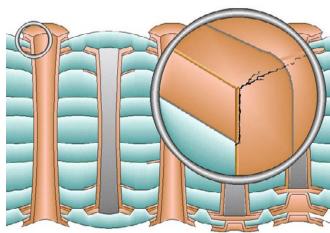

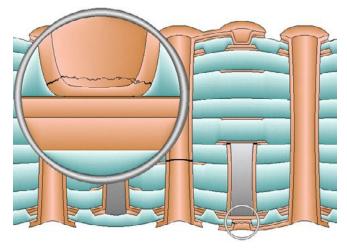

The most common type of failure of a robust interconnection is a barrel crack that occurs in the central zone of the plated through hole (PTH). When tested using thermal cycling to 150°C, this is a wear-out type of failure that happens over

hundreds of cycles (500+ cycles). Surviving 500 cycles without any significant increase in resistance is considered a robust coupon.

In a weak coupon, the failure before 350 cycles may relate to a process problem, with the most common problem being thin copper plating. With thin plating, the barrel cracks may still be the cause the failure but it would be failing in less than 350 cycles. The PTH may also fail for corner cracks or interconnection separation.

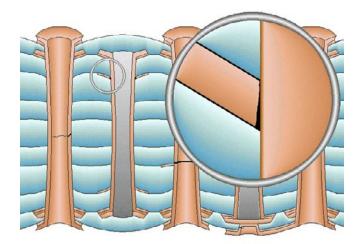

Weak buried vias fail typically with barrel cracks in the center zone of the structure similar to PTHs and, less often, with corner cracks or interconnect separation. One of the HDI structures includes microvias stacked on buried vias.

Figure 1: Barrel crack due to metal fatigue.

Figure 3: Corner or knee crack.

Figure 2: Interconnect separation.

Figure 4: Lifted copper cap on buried via.

" Providing Solutions to Board Fabrication Challenges"

## FROM CONCEPT TO COMPLETION

### **Solutions for Every Complex Situation**

At Multilayer Technology we have the skills and the knowledge to be able to say "Yes We Can!" to your most complex design requirements.

We specialize in High-Speed Digital and RF Design constraints. In addition, we offer the following solution-based services:

- Extensive Exotic Material Processing

- Pre-DFM Services Available

- State-of-the-Art Industry Leading Processes

- Space-Based Reliability Requirements Standard

**REQUEST A QUOTE**

3835 Conflans Rd Irving, TX 75061-3914

(972) 790-0062

### **HDI PWB RELIABILITY** continues

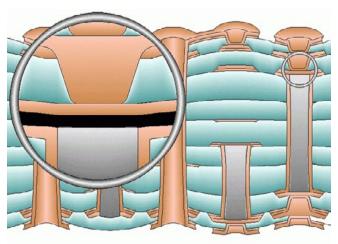

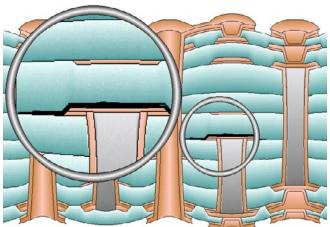

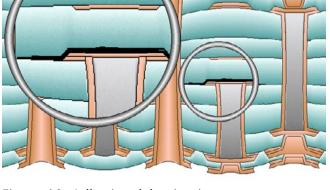

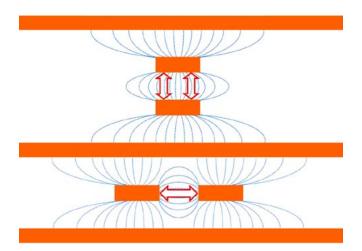

In order to have a microvia stacked on top of the buried via, what we have to have is a conductive cap on the top of the buried via, which can also fail. There may be a separation of the copper cap from the top of the buried via or a crack in the cap of the buried via (Figure 7).

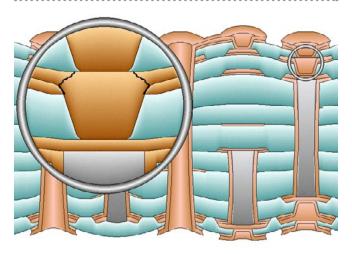

Microvias are typically the most robust type of interconnection. Because of their robustness, they are tested at 190°C. When tested at 190°C, robust microvias will survive 500 cycles while weak microvias will fail before 500 cycles. The most common cause of microvia failure is a separation between the base of the microvia and the target pad. The second most common cause of microvia failure is a barrel crack toward the base of the microvia. Other failure

modes include corner cracks (seen in copperfilled microvias) and pull out types of failures where the target pad cracks around the base of the microvia.

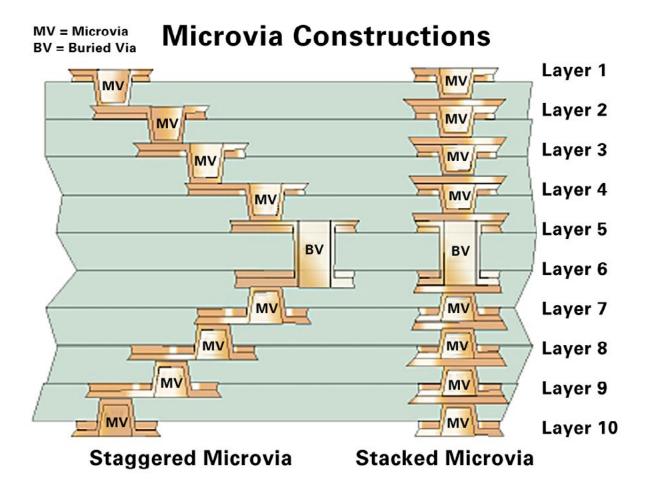

In HDI PWBs one must also consider construction. One may produce multiple microvias structures as either stacked or staggered. Microvias that are stacked are about four times more vulnerable to failure than the same structure in which the microvias are staggered. Well fabricated one- and two-layer microvias do not usually fail prematurely. Three- and four-stacked microvias tend to fail before 500 cycles when tested at 190°C and are a fabrication challenge.

The material damage is monitored in an IST coupon by measuring changes in capacitance

Figure 5: Microvia separation.

Figure 7: Microvia pull out failure.

Figure 6: Microvia barrel crack.

Figure 8: Microvia corner crack.

Our superior PCB, RF, and Hybrid design software guides you quickly and seamlessly from analysis to schematic to layout to manufacturing, with total design flexibility. Intercept's EDA environment solution includes powerful database translators for easy migration, full library support, advanced CAE/schematic design software, CAD/layout software, the industry's most powerful reuse block technology, and much more. Our customers achieve 100% manufacturability the first time.

PCB+HYBRID+RF DESIGN SOFTWARE, INCLUDING:

REUSE BLOCK TECHNOLOGY

MULTI-BOARD, PANEL ARRAYS

ARTWORK PANELIZATION

LAYOUT DRIVEN DESIGN & PROTOTYPING

INTERFACES TO SIMULATION & ANALYSIS

HIGH SPEED MATCHING, AUTO-TUNING

BIDIRECTIONAL RF INTERFACES

AUTOMATIC DRAWING CREATION

DESIGN AUTOMATION

DFM + MANUF. RULE CHECKING

ARTWORK VERIFICATION

www.intercept.com

Figure 9: Staggered vs. stacked microvias.

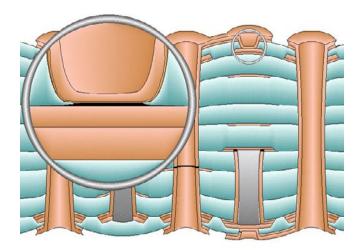

between ground layers in the coupon. First, measure the capacitance between two flooded ground planes in the coupons in the as-received state and then again after the coupon has undergone preconditioning, and at the end of test. If there is significant material damage then a -4% or greater drop in capacitance is seen. To confirm the drop in capacitance is indicative of material damage, one or two of the coupons are subjected to a microsection to check for the presence of material damage.

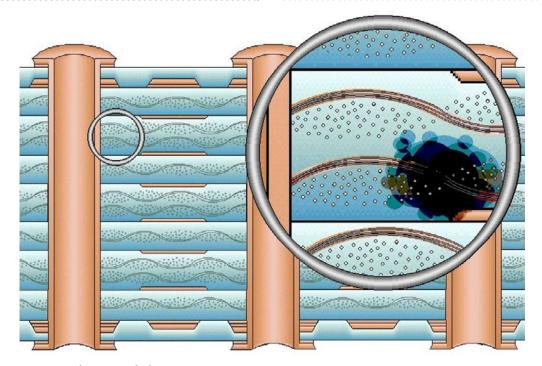

The major types of material damage found are adhesive delamination, cohesive cracks, and crazing. Adhesive delamination is typically between two laminated surfaces like the b-stage, c-stage and copper interfaces. On occasion, adhesive delamination is seen between the glass bundles as a group and epoxy of the dielectric. This type of failure is found typically on a 1 mm (.040") grid or greater.

The most common type of material damage is the cohesive crack, which is a crack that goes through the b-stage, c-stage and glass bundles. The cohesive failure is a breakdown of the epoxy system due to high temperatures of assembly. This type of failure is found typically on a 0.8 mm (.032") grid.

Crazing is the separation between glass fibers and the epoxy system. It looks like silver sheen on the glass bundles due to an envelope of air around the glass fiber. Crazing provides a pathway for conductive anodic filament (CAF) formation. This type of failure is found typically on a 0.5 mm (.020") grid.

### **HDI PWB RELIABILITY** continues

Figure 10: Adhesive delamination.

Figure 11: Cohesive crack.

Figure 12: Crazing with a CAF failure.

In conclusion, the use of HDI PWB reliability in lead-free applications is a dualedged sword. The copper interconnections are more prone to a breakdown and the material is more prone to damage. That is not to say that robust PWBs cannot be made, but there is a challenge in producing them. One must test the interconnect and the material in order to confirm robustness in a given application. **PCBDESIGN**

Paul Reid's career in PCB fabrication and reliability testing spans 35 years. One of his specialties is producing technical animations of failure modes induced by thermal excursions, giving

him insight into the mechanisms of circuit board failure. Reid is now retired. To contact the author, click here.

### **PCB007 News Highlights**

### Viasystems' Faces Challenging **Third Quarter**

"Regarding Viasystems' operating activities in the third quarter, we had to overcome several challenges, including a temporary work stoppage by employees in our largest factory in China, a sudden downturn of demand for products assembled in our Juarez, Mexico factory, and a temporary disruption in the supply chain for certain raw materials used to produce our printed circuit boards," says David M. Sindelar, CEO.

### **Dragon Circuits' Drone Division Experiments with Deliveries**

The company announces the successful completion of 14 autonomous and semi-autonomous delivery test runs with payloads ranging from a few ounces to a few pounds. With the recent interest in drone-based delivery by internet giants like Amazon and Google, Dragon Circuits looks to capitalize on a forthcoming demand with the expansion of their drone department.

### **TTM Reports Sequential Increase** in Q3 Revenue

Net sales for the third quarter of 2014 were \$345.3 million compared to \$297.6 million in the second quarter of 2014 and \$338.7 million in the third quarter of 2013.

### Q3 PCB/EMS Market Snapshot

I-Connect007's latest market survey—a one-minute survey designed to provide a snapshot of the current state of the PCB and EMS industries—offers a good sampling to give us a snapshot of where we've been and where we're headed.

### **IPC: N.A. September PCB Orders** Strengthened

"The North American PCB industry's solid sales and order growth over the previous month reflects normal seasonal patterns," said Sharon Starr, IPC's director of market research. "Despite strong order growth in September, orders continued to lag shipments by a small margin, pushing the PCB book-to-bill ratio just below parity."

### **MFLEX Rebounds in Q4, Expects** Sustained Growth

"We had a strong fiscal fourth quarter with net sales results at the high end of our guidance range, gross margin exceeding our guidance range, and a return to profitability, an important milestone for the company. Our net sales increased 32 percent sequentially, driven by new programs that ramped across our customer base," says Reza Meshain, CEO.

### AT&S Reports Improved Profitability in 1H of 2014/15

In the first six months of the financial year 2014/15 (April 1-September 30, 2014) leading PCB manufacturer AT&S generated revenue of EUR 302.1 million, which was in line with the high level of revenue reported for the same period last year (H1 2013/14: EUR 299.9 million).

### **Continental Named PACE Award Finalists for BD-HDI PCB**

Continental, a leading international automotive supplier, has three product innovations advancing as finalists in the 2015 Automotive News Premier Automotive Suppliers Contribution to Excellence (PACE) Award program.

### **SCHWEIZER Posts Strong 3014 Results**

"Our business results after the first nine months of this fiscal year are really satisfying and come up to our expectations. In the third quarter, successes in our portfolio management already had an important influence on the improved results compared to the second quarter," says Dr. M. Schweizer, CEO Schweizer Electronic AG.

### **Aspocomp Reports Positive 2014 Amid Q3 Sales Drop**

Deliveries slowed down significantly in July-September, and third-quarter net sales amounted to EUR 4.9 million, a year-on-year decrease of EUR 0.3 million. Sales decreased mainly because telecommunication customers had placed over-large orders at the beginning of the year.

## Unsurpassed Quality. Cutting Edge Technology.

AS9100, MIL-PRF-55110, and MIL-P-50884 Certified for Rigid, Flex and Rigid-Flex Printed Circuit Board Fabrication.

#### by Kenneth MacCallum

STARFISH MEDICAL

This article originally ran in the November 2014 issue of The PCB Magazine.

#### Introduction

PCBs are an increasingly important part of modern medical devices—especially electromechanical devices. The opportunities are large, but PCB designers and manufacturers must be aware of and work within the regulations and limitations in the medical device design process. This article will provide an overview of the medical device design process, the role of PCBs in that process and in modern medical devices, and include design considerations and tips for incorporating PCBs into medical devices.

#### **Medical Device Design Process**

The medical device development industry is heavily regulated. Not only are the charac-

teristics and performance of the devices regulated, the design and development processes are as well. The focus is on well-defined and understood requirements, quantification of risk of harm to patient and operator, verification that the design meets the specifications and finally validation that the design is effective and safe.

Many medical devices are manufactured in lower volume than consumer electronics and have higher margins; and most have longer design cycles. Notwithstanding these differences, the technologies used in medical devices are often heavily leveraged from consumer electronics. This means the same creep towards higher density circuits and component packaging applies in the medical field. The same techniques of replacing wiring harnesses with PCBs and flex circuits that are found in consumer electronics are found in medical devices, although the drive towards these technologies may be increased reliability and reduced labour cost instead of decreased size and reduced parts cost.

## Solutions to Ensure PCB Manufacturing Success!

#### **CAM350**

Verify and Optimize PCB Designs for Successful Manufacturing.

#### BluePrint PCB

Create comprehensive documentation to drive PCB fabrication, assembly and inspection.

#### **DFMStream**

Verify Design and Manufacturing Rules Any Time During the PCB Design Cycle.

At DownStream Technologies we are committed to delivering comprehensive solutions and workflow process improvements for all your PCB post processing needs.

For more information please visit downstreamtech.com or call 800-535-3226.

Once the sub-circuit

layouts are routed, these

are then pushed and

shoved together like

puzzle pieces. It is helpful

to minimize the number

of layers of sub-circuits

even if the board

#### PCBS FOR MEDICAL APPLICATIONS—A DESIGNER'S PERSPECTIVE continues

#### **Role of PCBs in Medical Devices**

Almost every medical device PCB is heavily influenced and constrained by the work of other disciplines. It is rare that a board can be designed without heavy consultation throughout the design cycle with mechanical engineers or industrial designers. There is usually no clear owner to the mechanical constraints of a PCB. A board outline may be proposed, then shoehorned as the housing design gets hashed out. Rearranged as the main, large components, connectors and things get roughly placed; it will be tweaked again by the mechanical engineers or industrial designers. Finally the PCB designer will add their final touches and throw it back. This process is highly iterative and relies more and more on accurate 3D modeling of the board, connectors and wiring.

will be manufactured PCBs are structural elewith many. ments with all sorts of great mechanical properties: they are fairly rigid, they're pretty strong and their tolerances are often excellent. The collaboration doesn't stop there either. Whoever is doing the firmware, software and logic design will also have some strong opinions about the board. It's best to get everyone together early and often to minimize the chance of later rework or worse.

Medical devices have some of strictest industry EMC requirements and regulations. Addressing these constraints is primarily achieved at the PCB level. This is yet another factor driving PCB density and manufacturing tolerances.

#### **Design Considerations and Tips**

As PCBs in medical devices become more complex and dense, it is more important than ever to ensure that the designs are correct and will function as required. Although a typical medical product will see three or more significant PCB design cycles it is important that the value of each cycle is maximized. The more functionality is designed into a board, the more possibilities for errors and faults there is.

#### **General Rules**

Electronic design automation (EDA) software now has sophisticated automatic designrule checking, providing the rules are set up properly. These cannot prevent a bad design from getting into production, but they can prevent very common and frequent mistakes and oversights from getting out.

As PCBs get more complicated, it is helpful to partition designs hierarchically.

> The top level of a hierarchical design is much like a block diagram of the board. Putting all connectors on the top level schematic sheet if possible, makes that sheet very useful during troubleshooting and design reviews. Child sheets encapsulate lower level functionality and sub-circuits. These can be referenced multiple times if a circuit is repeated, rather than cut and pasted as separate sheets. This allows for easier duplication of layout and is less prone to mistakes creeping in.

Once the schematic design is done, sub-circuits are often routed first, without constraining them to the board outline. This leads to a better overall layout compared to the traditional approach of component placement followed by routing. Once the sub-circuit layouts are routed, these are then pushed and shoved together like puzzle pieces. It is helpful to minimize the number of layers of sub-circuits even if the board will be manufactured with many. This makes it easier to re-use portions of layouts or adapt to last minute changes in layer counts.

More and more boards have high frequency differential pairs or impedance critical singleended signals. Use a finite element analysis (FEA) calculator to determine the correct trace width and spacing. FEA gives more flexibility than the analytical solutions although they are often not far off each other. Do not neglect the effects of adjacent ground pours or traces. If you are unable to guarantee the impedance to the closest plane layer then adjacent ground pours are a nice way to control the impedance. Make sure

#### PCBS FOR MEDICAL APPLICATIONS—A DESIGNER'S PERSPECTIVE continues

to stitch the pour to the ground plane all along the controlled impedance traces. These calculations can then be compared with the controlled impedance results from the PCB manufacturer.

Unfortunately, the industry standard for PCB manufacturing files is still the old Gerber format. These files never contain quite enough information to be sure the boards will turn out right. They don't contain units, the decimal place can be ambiguous and even the origin is uncertain. It is good practice to disable zero suppression, and use an absolute origin for both Gerbers and drill files. It is also good practice to inspect all files with Gerber viewing software other than the EDA package that generated them. More and more PCB manufacturers now have automated workflows with little human intervention or interaction. Layer misalignment or scaling issues can sneak right through the manufacturing process and only be found when the boards are done.

#### Strategies for Planes and Pours

It is a good strategy to flood planes rather than using single net planes. This provides the benefit of allowing the odd trace to route on that layer in a pinch. It also makes it easier to segregate power rails, separate planes and avoid interference with impedance controlled traces. Although it made sense in the days of limited file sizes and taped layouts to route planes as negatives, now this just seems like a source of errors either in review or manufacture.

Due to modern boards having many voltage rails, it is rarely advantageous or even possible to use complete power planes other than for ground. Instead, one or a few layers can be dedicated to power routing using fills and fat traces. As a bonus, signals can be snuck through on these layers as well. When pulling power off onto the component layers, it should first hit one or more bypass capacitors with the other pin drilled to ground, then the destination component pin.

Ensure flooded regions are stitched well to others. This is especially important on a two layer board where planes are impossible and ground is really just a collection of pours and is quite broken up. Pours should be kept away from controlled impedance traces unless they are part of the controlled impedance strategy. If they are, then they should be well bypassed to ground. Note that impedance controlled traces crossing over fill boundaries will experience impedance discontinuities. These boundaries should be stitched either with vias to other layers or with bypass caps across the gap. This stitching should occur as close to the traces as possible.

It is often problematic to break planes into regions like analog signal ground or power ground. Having one good plane that is well decoupled to the chassis can be better than breaking planes up into different power regions. The effects and locations of high frequency switching currents should be carefully considered and controlled. If possible, keep them off the plane. If a plane must be broken into different regions, a line of no-fit caps should be added, just in case.

Consideration should be given to the currents of various sub-circuits that will flow through the plane and their impact on other subcircuits along the way. A slight void or cut in the plane to explicitly corral these currents can be an effective strategy to control them. Sometimes a different arrangement of sub-circuits will give even better results.

#### **Layout EMC Considerations**

Given that medical devices are heavily regulated, at some point electromagnetic compatibility will have to be considered. Add ESD & EMC reduction components like TVS diodes and ferrites, even if the board is a prototype with no plans for EMC testing. This provides a head start to flush out problems early. It also plans ahead for a prototype being used beyond what was initially imagined or intended. Consider designing in the parts without populating them right away. Then they can be easily added later without cutting and gluing.

Consider where noise may come from both on and off of the PCB. Reducing noise at the source is always a better strategy than combatting it only where it is creating trouble. An example of this is the high speed parallel lines to a TFT display. A tidy bank of ferrites right at the driver outputs is often all it needs. This is easiest done at the PCB design stage.

looking simulation

results from a situation

which would vaporize

parts in a microsecond.

Similarly, the system

modeled might ignore

a part's non-ideality or

a parasitic signal path

that occurs in reality

and critically affects

performance.

#### PCBS FOR MEDICAL APPLICATIONS—A DESIGNER'S PERSPECTIVE continues

When laying out switch-mode power supplies or filters on PWM circuits, designers should think about high-frequency current paths-there are usually two of them-and keep the area of these paths minimized. This usually means placing the big components first: switches, inductors, caps and diodes.

Only connect switch-mode supply and PWM filter circuits to the rest of the PCB ground in one place. This includes signal grounds to the control ICs. Use the ground terminal of the main input capacitor. If the connection is done in more than one location, the ground plane and hence other circuits may be polluted with switching currents. Be wary of nearby copper pours accidentally touching the ground One can get valid net somewhere else.

#### **Simulation**

Given the investment in time and effort to design PCBs it pays to simulate in order to learn as much as possible prior to the board order. Usually this does not mean simulating a whole circuit but focuses on key sub-circuits, or even key components of these sub-circuits.

A good candidate for simu-

lation is to validate the choice of switch-mode power supply inductor. If the inductor is poorly chosen the circuit will smoke. Typical equation-based methods for determining the peak current requirements often are optimistic. A quick simulation regularly shows that under certain conditions the current will go just a bit higher. Simulate at worst-case conditions: maximum current, minimum inductance, maximum input voltage, etc. This determines the peak inductor current, which is often much higher than expected.

Simulation is also very useful in developing feedback systems. In medical devices it's not unusual for a control system to have hundreds of Watts at its disposal. To rush to experimentation in such a system is likely to result in damaged parts or even injuries